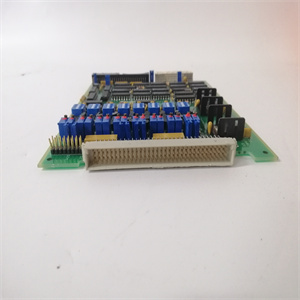

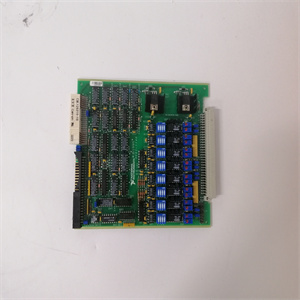

产品展示

联系我们

联系人:麦女士

手机:+86 15270269218

电话:

Q Q:3136378118

邮箱:stodcdcs@gmail.com

地址:江西省九江市瑞昌市东益路23号赛湖农商城401号

NI PCI-6517(32路漏极输出)

外部时钟采集,NI-DAQ不知道何时获取后一个点,因此必须提供三个额外的脉冲。CONVERT*信号任何PFI引脚都可以接收CONVERT*信号作为输入,该信号可作为PFI2/CONVERT*引脚上的输出。CONVERT*与DAQ序列的关系见图4-9和4-10。作为输入,CONVERT*在边缘检测模式下配置。您可以选择任何PFI引脚作为转换*的源,并配置上升沿或下降沿的极性选择。CONVERT*的选定边缘启动A/D转换。作为输出,CONVERT*反映连接到ADC的实际转换脉冲,即使另一个PFI在外部生成转换。输出为有效低脉冲,脉冲宽度为50至100 ns。该输出在启动时设置为高阻抗。图4-17和4-18显示了转换*的计时要求。图4-17:。CONVERT*输入信号定时上升沿极性下降沿极性t w t w=10 ns小值4章连接信号©National Instruments Corporation 4-25 NI PCI-6110/6111用户手册图4-18。CONVERT*输出信号定时ADC切换到保持模式,距离选定边缘20 ns以内。该保持模式延迟时间是温度的函数,在一次转换到下一次转换时不会变化。除非您选择一些外部源,否则NI PCI-6110/6111上的SI2通常会生成CONVERT*。计数器由STARTSCAN信号启动,继续并重新加载,直到扫描完成。然后,它重新加载自己,为下一个STARTSCAN脉冲做好准备。由内部或外部CONVERT*信号生成的A/D转换被禁止,除非它们发生在DAQ序列中。DAQ序列中发生的扫描可通过硬件(AIGATE)信号或软件命令寄存器门进行选通。AIGATE信号任何PFI引脚都可以接收AIGATE信号作为输入,AIGATE信号不能作为输入/输出连接器上的输出。AIGATE信号可以在DAQ序列中屏蔽扫描。您可以在电平检测或边缘检测模式下配置您选择作为AIGATE信号源的PFI引脚。您可以将PFI引脚的极性选择配置为激活高电平或激活低电平。在液位检测模式下,如果AIGATE处于激活状态,STARTSCAN信号将被屏蔽,并且不会发生扫描。在边缘检测模式下,一条活动边缘禁用STARTSCAN信号,二条活动边缘启用STARTSCAN。AIGATE既不能停止正在进行的扫描,也不能继续以前的选通关闭扫描。一旦扫描开始,AIGATE在下一次扫描开始之前不会关闭转换,相反,如果

externally clocked acquisition, NI-DAQ does not know when the last point is taken, so you must provide the three extra pulses. CONVERT* Signal Any PFI pin can receive as an input the CONVERT* signal, which is available as an output on the PFI2/CONVERT* pin. Refer to Figures 4-9 and 4-10 for the relationship of CONVERT* to the DAQ sequence. As an input, CONVERT* is configured in the edge-detection mode. You can select any PFI pin as the source for CONVERT* and configure the polarity selection for either rising or falling edge. The selected edge of CONVERT* initiates an A/D conversion. As an output, CONVERT* reflects the actual convert pulse that is connected to the ADC, even if another PFI is externally generating the conversions. The output is an active low pulse with a pulse width of 50 to 100 ns. This output is set to high-impedance at startup. Figures 4-17 and 4-18 show the timing requirements for CONVERT*. Figure 4-17. CONVERT* Input Signal Timing Rising-edge polarity Falling-edge polarity t w t w = 10 ns minimum Chapter 4 Connecting Signals © National Instruments Corporation 4-25 NI PCI-6110/6111 User Manual Figure 4-18. CONVERT* Output Signal Timing The ADC switches to hold mode within 20 ns of the selected edge. This hold-mode delay time is a function of temperature and does not vary from one conversion to the next. The SI2 on the NI PCI-6110/6111 normally generates CONVERT* unless you select some external source. The counter is started by the STARTSCAN signal and continues to count down and reload itself until the scan is finished. It then reloads itself in preparation for the next STARTSCAN pulse. A/D conversions generated by either an internal or external CONVERT* signal are inhibited unless they occur within a DAQ sequence. Scans occurring within a DAQ sequence may be gated by either the hardware (AIGATE) signal or software command register gate. AIGATE Signal Any PFI pin can receive as an input the AIGATE signal, which is not available as an output on the I/O connector. The AIGATE signal can mask off scans in a DAQ sequence. You can configure the PFI pin you select as the source for the AIGATE signal in either the level-detection or edge-detection mode. You can configure the polarity selection for the PFI pin for either active high or active low. In the level-detection mode if AIGATE is active, the STARTSCAN signal is masked off and no scans can occur. In the edge-detection mode, the first active edge disables the STARTSCAN signal, and the second active edge enables STARTSCAN. AIGATE can neither stop a scan in progress nor continue a previously gated-off scan. Once a scan has started, AIGATE does not gate off conversions until the beginning of the next scan and, conversely, if

相关产品