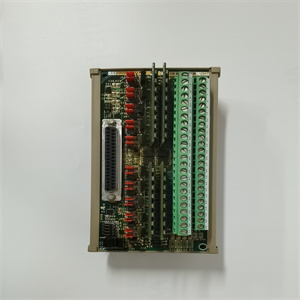

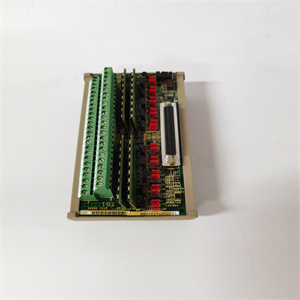

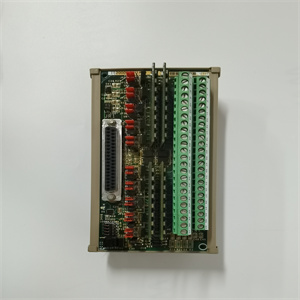

产品展示

联系我们

联系人:麦女士

手机:+86 15270269218

电话:

Q Q:3136378118

邮箱:stodcdcs@gmail.com

地址:江西省九江市瑞昌市东益路23号赛湖农商城401号

VMIVME-1181-000

读取此字段时,当前计数值被锁定并返回。有两个

根据“Read”(读取)的设置确定如何锁存计数的模式

锁存WDT控制状态寄存器(CSR2)中的“选择”位。参见CSR2寄存器

有关这两种模式的更多信息,请参阅说明。

定时器4电流计数寄存器(TMRCCR4)

定时器4的当前计数可通过定时器4电流计数寄存器读取

(TMRCCR4),位于BAR2中地址的偏移量0x28处。中的位映射

该登记册如下:

读取此字段时,当前计数值被锁定并返回。有两个

根据“Read”(读取)的设置确定如何锁存计数的模式

锁存WDT控制状态寄存器(CSR2)中的“选择”位。参见CSR2寄存器

有关这两种模式的更多信息,请参阅说明。

定时器1 IRQ清除(T1IC)

定时器1 IRQ Clear(T1IC)寄存器用于清除定时器1引起的中断。

写入该寄存器(位于BAR2中地址的偏移量0x30处)会导致

定时器1的中断被清除。也可以通过将“0”写入

定时器控制状态寄存器(CSR1)的相应“定时器x导致IRQ”字段。

该寄存器仅写,写入的数据不相关。

定时器2 IRQ清除(T2IC)

定时器2 IRQ Clear(T2IC)寄存器用于清除定时器2引起的中断。

写入该寄存器(位于BAR2中地址的偏移量0x34处)会导致

定时器2的中断被清除。也可以通过将“0”写入

定时器控制状态寄存器(CSR1)的相应“定时器x导致IRQ”字段。

此寄存器为只写寄存器,写入的数据不相关。

定时器3 IRQ清除(T3IC)

定时器3 IRQ清除(T3IC)寄存器用于清除定时器3引起的中断。

写入该寄存器(位于BAR2中地址的偏移量0x38处)会导致

定时器3的中断被清除。也可以通过将“0”写入

定时器控制状态寄存器(CSR1)的相应“定时器x导致IRQ”字段。

此寄存器为只写寄存器,写入的数据不相关。

读取或写入字段位

计时器4计数TMRCCR4[31..0]R.O。

When this field is read, the current count value is latched and returned. There are two modes that determine how the count is latched depending on the setting of the “Read Latch Select” bit in the WDT Control Status Register (CSR2). See the CSR2 register description for more information on these two modes. Timer 4 Current Count Register (TMRCCR4) The current count of Timer 4 may be read via the Timer 4 Current Count Register (TMRCCR4), located at offset 0x28 from the address in BAR2. The mapping of bits in this register are as follows: When this field is read, the current count value is latched and returned. There are two modes that determine how the count is latched depending on the setting of the “Read Latch Select” bit in the WDT Control Status Register (CSR2). See the CSR2 register description for more information on these two modes. Timer 1 IRQ Clear (T1IC) The Timer 1 IRQ Clear (T1IC) register is used to clear an interrupt caused by Timer 1. Writing to this register, located at offset 0x30 from the address in BAR2, causes the interrupt from Timer 1 to be cleared. This can also be done by writing a “0” to the appropriate “Timer x Caused IRQ” field of the timer Control Status Register (CSR1). This register is write only and the data written is irrelevant. Timer 2 IRQ Clear (T2IC) The Timer 2 IRQ Clear (T2IC) register is used to clear an interrupt caused by Timer 2. Writing to this register, located at offset 0x34 from the address in BAR2, causes the interrupt from Timer 2 to be cleared. This can also be done by writing a “0” to the appropriate “Timer x Caused IRQ” field of the timer Control Status Register (CSR1). This register is write only and the data written is irrelevant. Timer 3 IRQ Clear (T3IC) The Timer 3 IRQ Clear (T3IC) register is used to clear an interrupt caused by Timer 3. Writing to this register, located at offset 0x38 from the address in BAR2, causes the interrupt from Timer 3 to be cleared. This can also be done by writing a “0” to the appropriate “Timer x Caused IRQ” field of the timer Control Status Register (CSR1). This register is write only and the data written is irrelevant. Field Bits Read or Write Timer 4 Count TMRCCR4[31..0] R.O.

相关产品